# **MODULE -1**

# **OVERVIEW OF DIGITAL DESIGN WITH VERILOG HDL**

# 1.1: Objectives

- > Understand the importance and trends of HDL.

- > Understand the design flow and design methodologies for digital design.

- > Explain the difference between modules and module instances in Verilog.

- > Describe four levels of abstraction and define stimulus block and design block.

# **1.2 Evolution of Computer-Aided Digital Design**

In early days digital circuits were designed with vacuum tubes and transistor. Then integrated circuits chips were invented which consists of logic gates embed on them. As technology advances from SSI (Small Scale Integration), MSI (Medium Scale Integration), LSI (Large Scale Integration), designers could implement thousands of gates on a single chip. So the testing of circuits and designing became complicated hence Electronic Design Automation (EDA) techniques to verify functionality of building blocks were one.

The advances in semiconductor technology continue to increase the power and complexity of digital systems with the invent of VLSI (very Large Scale Integration) with more than 10000 transistors. Because of the complexity of circuit, breadboard design became impossible and gave rise to computer aided techniques to design and verify VLSI digital circuits. These computer aided programs and tools allow us to design, do automatic placement and routing and Abe to develop hierarchical based development and hence prototype development by downloading of programmable chips (like - ASIC, FPGA, CPLD) before fabrication.

# **1.3 Emergence of HDLs**

In the field of digital design, the complexity in designing a circuit gave birth to standard languages to describe digital circuits (ie. Hardware Description Languages - HDL). HDL is a Computer Aided design (CAD) tool for the modern design and synthesis of digital systems. HDLs were been used to model hardware elements very concurrently. Verilog HDL and VHDL are most popular HDLs.

In initial days of HDL, designing and verification were done using tool but synthesis (ie translation of RTL to schematic circuit) used to be done manually which become tediously as technology advances. Later

tool is automated to generate the schematic of RTL developed.

Digital circuits are described at Registers Transfer Level (RTL) by using HDL. Then logic synthesis tool will generate details of gates and interconnection to implement circuits. This synthesized result can be used for fabrication by having placement and routing details. Verify functionality using simulation. HDLs are used for system-level design - simulation of system boards, interconnect buses, FPGAs and PALs. Verilog HDL is IEEE standard - IEEE 1364-2001.

Note: RTL - designer has to specify how the data flows between registers and how the design processes the data.

# **1.4 Typical Design Flow**

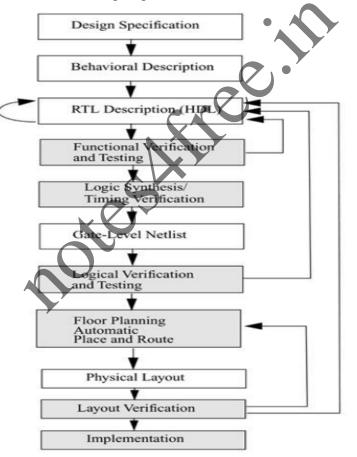

A typical design flow (HDL flow) for designing VLSI IC circuits is as shown in figure 1.1

Figure: 1.1: Typical design flow

The design flow in any design, specifications are written first. Specifications describe abstractly the functionality, interface, and overall architecture of the digital circuit to be designed. At this point, the architects

do not need to think about how they will implement this circuit. A behavioral description is then created to analyze the design in terms of functionality, performance, and compliance to standards, and other high-level issues. Behavioral descriptions are often written with HDLs.

New EDA tools have emerged to simulate behavioral descriptions of circuits. These tools combine the powerful concepts from HDLs and object oriented languages such as C++. These tools can be used instead of writing behavioral descriptions in Verilog HDL. The behavioral description is manually converted to an RTL description in an HDL. The designer has to describe the data flow that will implement the desired digital circuit. From this point onward, the design process is done with the assistance of EDA tools.

Logic synthesis tools convert the RTL description to a gate-level net list. Logic synthesis tools ensure that the gate-level net list meets timing, area, and power specifications.

A gate-level net list is a description of the circuit in terms of gates and connections between them. The gate-level net list is input to an Automatic Place and Route tool, which creates a layout.

The layout is verified and then fabricated on a chip.

Thus, most digital design activity is concentrated on manually optimizing the RTL description of the circuit. After the RTL description is frozen, EDA tools are available to assist the designer in further processes. Designing at the RTL level has shrunk the design cycle times from years to a few months. It is also possible to do many design iterations in a short period of time.

Behavioral synthesis tools have begun to emerge recently. These tools can create RTL descriptions from a behavioral or algorithmic description of the circuit. As these tools mature, digital circuit design will become similar to high-level computer programming. Designers will simply implement the algorithm in an HDL at a very abstract level. EDA tools will help the designer convert the behavioral description to a final IC chip.

# **1.5 Importance of HDLs**

HDLs have many advantages that help in developing large digital circuits reaching the optimized circuit design.

• Designs can be described at a very abstract level by use of HDLs. Designers can write their RTL description without choosing a specific fabrication technology. Logic synthesis tools can automatically convert the design to any fabrication technology. If a new technology emerges, designers do not need to redesign their circuit. They simply input the RTL description to the logic synthesis tool and create a new gate-level netlist, using the new fabrication technology. The logic synthesis tool will optimize the

circuit in area and timing for the new technology.

- By describing designs in HDLs, functional verification of the design can be done early in the design cycle. Since designers work at the RTL level, they can optimize and modify the RTL description until it meets the desired functionality. Most design bugs are eliminated at this point. This cuts down design cycle time significantly because the probability of hitting a functional bug at a later time in the gate-level netlist or physical layout is minimized.

- Designing with HDLs is similar to computer programming. A textual description with comments is an easier way to develop and debug circuits. This also provides a concise representation of the design, compared to gate-level schematics. Gate-level schematics are almost incomprehensible for very complex designs.

- Verilog HDL is a general-purpose hardware description language that is easy to learn and easy to use. It is similar in syntax to the C programming language. Designers with C programming experience will find it easy to learn Verilog HDL.

- Verilog HDL allows different levels of abstraction to be mixed in the same model. Thus, a designer can define a hardware model in terms of switches, gates, RTL, or behavioral code. Also, a designer needs to learn only one language for stimulus and hierarchical design. Most popular logic synthesis tools support Verilog HDL. This makes it the language of choice for designers.

- All fabrication vendors provide Verilog HDL libraries for post-logic synthesis simulation. Thus, designing a chip in Verilog HDL allows the widest choice of vendors.

- The Programming Language Interface (PLI) is a powerful feature that allows the user to write custom C code to interact with the internal data structures of Verilog. Designers can customize a Verilog HDL simulator to their needs with the PLI.

# **1.6 Trends in HDLs**

Increase in speed and complexity go digital circuits will complicate the designer job, but EDA tools make the job easy for designer. Designer has to do high level abstraction designing and need to take care of functionality of the design and EDA tools take care of implementation, and can achieve a almost optimum design.

Digital circuits are designed in HDL at an RTL level, so that logic synthesis tools can create gate level net lists. Behavioral synthesis allowed designers to directly design in terms of algorithms and the behavior of the circuit EDA tool is then used to translate and optimize at each phase of design. Verilog HDL is also used widely for verification. Formal verification uses mathematical techniques to verify the correctness of Verilog HDL descriptions and to establish equivalency between RTL and gate level net lists. Assertion checking is done to check the transition and important parts of a design.

# **1.7 Design Methodologies**

There are two basic types of digital design methodologies: a top-down design methodology and a bottom-up design methodology.

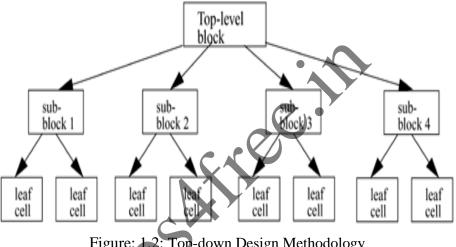

# **1.7.1 Top-down design methodology:**

This designing approach allows early testing, easy change of different technologies, a well structures system design and offers many other advantages.

Figure: 1.2: Top-down Design Methodology

In this method, top-level block is defined and sub-blocks necessary to build the top-level block are identified. We further subdivide, sub-blocks until cells cannot be further divided, we call these cells as leaf cells is as shown in figure 1.2.

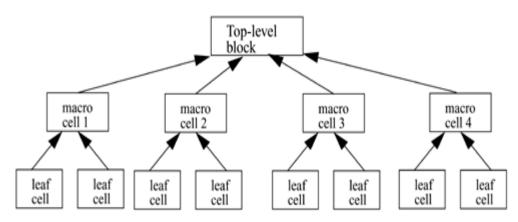

# 1.7.2 Bottom-up design methodology:

We first identify the available building blocks and try to build bigger cells out of these, and continue process until we reach the top-level block of the design is as shown in figure 1.3

Most of the time, the combination of these two design methodologies are used to design. Logic designers decide the structure of design and break up the functionality into blocks and sub blocks. And designer will design a optimized circuit for leaf cell and using these will design top level design.

Figure 1-3. Bottom-up Design Methodology

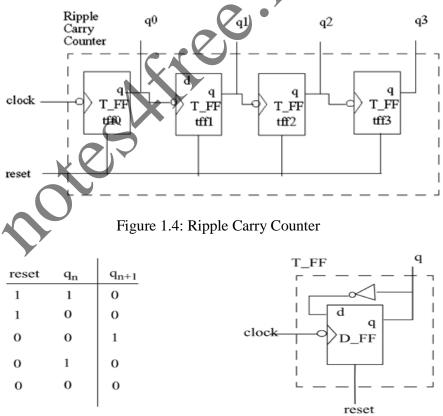

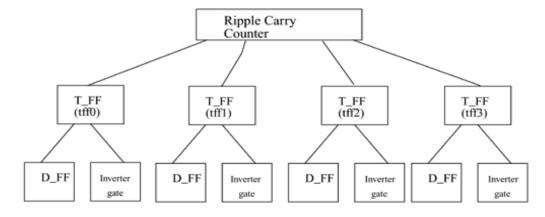

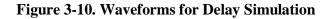

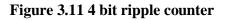

A hierarchical modeling concept is illustrated with an example of 4-bit Ripple Carry Counter.

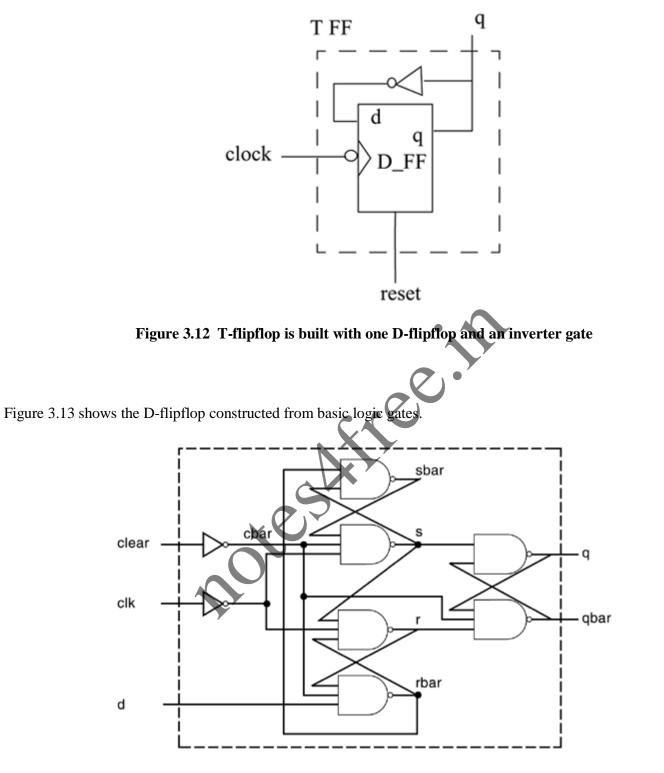

The ripple carry counter shown in Figure 1.4 is made up of negative edge-triggered toggle flip-flops (T\_FF). Each of the T\_FFs can be made up from negative edge-triggered D-flip-flops (D\_FF) and inverters (assuming q\_bar output is not available on the D\_FF), as shown in Figure 1.5.

Figure 1-5: T-flip-flop

Thus, the ripple carry counter is built in a hierarchical fashion by using building blocks. The diagram for the

design hierarchy is shown in Figure 1.6.

Figure 1.6. Design Hierarchy

In a top-down design methodology, we first have to specify the functionality of the ripple carry counter, which is the top-level block. Then, we implement the counter with T\_FFs. We build the T\_FFs from the D\_FF and an additional inverter gate. Thus, we break bigger blocks into smaller building subblocks until we decide that we cannot break up the blocks any further.

A bottom-up methodology flows in the opposite direction. We combine small building blocks and build bigger blocks; e.g., we could build D\_FF from and/or gates, or we could build a custom D\_FF from transistors. Thus, the bottom-up flow meets the top-down flow at the level of the D\_FF.

# 1.8 Modules

Verilog provides the concept of a module 'A module is the basic building block in Verilog. A module can be an element or a collection of lower level design blocks. Typically, elements are grouped into modules to provide common functionality that is used at many places in the design. A module provides the necessary functionality to the higher-level block through its port interface (inputs and outputs), but hides the internal implementation. This allows the designer to modify module internals without affecting the rest of the design. In Verilog, a module is declared by the keyword module. A corresponding keyword endmodule must appear at the end of the module definition.

module <module\_name> (<module\_terminal\_list>);

<module internals>

... endmodule

...

Specifically, the T-flipflop could be defined as a module as follows: module T\_FF (q, clock, reset);

<functionality of T-flipflop>

endmodule

Verilog is both a behavioral and a structural language. Internals of each module can be defined at four levels of abstraction, depending on the needs of the design. The levels are defined below.

• **Behavioral or algorithmic level:** This is the highest level of abstraction provided by Verilog HDL. A module can be implemented in terms of the desired design algorithm without concern for the hardware implementation details. Designing at this level is very similar to C programming.

• **Dataflow level:** At this level, the module is designed by specifying the data flow. The designer is aware of how data flows between hardware registers and how the data is processed in the design.

• Gate level: The module is implemented in terms of logic gates and interconnections between these gates. Design at this level is similar to describing a design in terms of a gate-level logic diagram.

• Switch level: This is the lowest level of abstraction provided by Verilog. A module can be implemented in terms of switches, storage nodes, and the interconnections between them. Design at this level requires knowledge of switch-level implementation details.

Verilog allows the designer to mix and match all four levels of abstractions in a design.

# **1.9 Module Instances:**

A module provides a template from which you can create actual objects. When a module is invoked, Verilog creates a unique object from the template. Each object has its own name, variables, parameters, and I/O interface. The process of creating objects from a module template is called instantiation, and the objects are called instances.

In Example of 4 bit ripple carry counter, the top-level block creates four instances from the T-flipflop (T\_FF) template. Each T\_FF instantiates a D\_FF and an inverter gate. Each instance must be given a unique name. Note that // is used to denote single-line comments.

#### **Example of Module Instantiation**

// Define the top-level module called ripple carry

// counter. It instantiates 4 T-flipflops. Interconnections are shown in figure 1.4 :4-bit Ripple Carry Counter.

module

ripple\_carry\_counter(q, clk, reset);

output [3:0] q; //I/O signals and vector declarations input clk, reset; //I/O signals will be explained later.

//Four instances of the module T\_FF are created. Each has a unique name. //Each instance is passed a set of signals. Notice, that each instance is a copy of the module T\_FF. T\_FF tff0(q[0],clk, reset); T\_FF tff1(q[1],q[0], reset); T\_FF tff2(q[2],q[1], reset); T\_FF tff3(q[3],q[2], reset); endmodule

enumodule

// Define the module T\_FF. It instantiates a D-flipflop.

//We assumed that module D-flipflop is defined elsewhere in the design.

//Refer to Figure 1-5 for interconnections.

module T\_FF(q, clk, reset);

output q;

input clk, reset;

wire d;

D\_FF dff0(q, d, clk, reset); // Instantiate D\_FF. Call it dff0. not n1(d, q); // not gate is a Verilog primitive. endmodule

In Verilog, it is illegal to nest modules. One module definition cannot contain another module definition within the module and endmodule statements.

reei

Example below shows an illegal module nesting where the module T\_FF is defined inside the module definition of the ripple carry counter.

#### Example for Illegal Module Nesting

// Define the top-level module called ripple carry counter.

// It is illegal to define the module T\_FF inside this module.

module ripple\_carry\_counter(q, clk, reset);

output [3:0] q;

input clk, reset;

#### module T\_FF(q, clock, reset);// ILLEGAL MODULE NESTING

```

•••

```

<module T\_FF internals>

```

...

```

endmodule // END OF ILLEGAL MODULE NESTING endmodule

# **1.20** Components of a Simulation

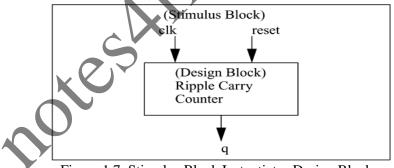

Once a design block is completed, it must be tested. The functionality of the design block can be tested by applying stimulus and checking results. We call such a block the stimulus block. It is good practice to keep the stimulus and design blocks separate. The stimulus block can be written in Verilog. A separate language is not required to describe stimulus. The stimulus block is also commonly called a test bench. Different test benches can be used to thoroughly test the design block.

Two styles of stimulus application are possible. In the first style, the stimulus block instantiates the design block and directly drives the signals in the design block. In Figure 1-7, the stimulus block becomes the top-level block. It manipulates signals clk and reset, and it checks and displays output signal q.

Figure 1.7. Stimulus Block Instantiates Design Block

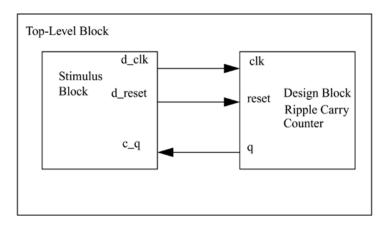

The second style of applying stimulus is to instantiate both the stimulus and design blocks in a top- level dummy module. The stimulus block interacts with the design block only through the interface. This style of applying stimulus is shown in Figure 1-8. The stimulus module drives the signals d\_clk and d\_reset, which are connected to the signals clk and reset in the design block. It also checks and displays signal c\_q, which is connected to the signal q in the design block. The function of top-level block is simply to instantiate the design and stimulus blocks. Either stimulus style can be used effectively.

Figure 1.8. Stimulus Block and Design Block Instantiated in a dummy toplevel module

# 1.21 Example

Consider the example of simulation of a ripple carry counter. We will define the design block and the stimulus block. We will apply stimulus to the design block and monitor the outputs.

# 1.21.1 Design Block

Consider a top-down design methodology. First, we write the Verilog description of the top-level design block which is the ripple carry counter.

# Example of Ripple Carry Counter Top Block

module ripple\_carry\_counter(q, clk, reset output [3:0] q;

input clk, reset;

//4 instances of the module T\_FF are created.

T\_FF tff0(q[0],clk, reset);

T\_FF tff1(q[1],q[0], reset);

T\_FF tff2(q[2],q[1], reset);

T\_FF tff3(q[3],q[2], reset);

endmodule

In the above module, four instances of the module  $T_FF$  (T-flipflop) are used. Therefore, we must now define the internals of the module  $T_FF$ .

#### Verilog HDL [15EC53]

#### **Example for Flipflop T\_FF**

module T\_FF(q, clk, reset); output q; input clk, reset; wire d; D\_FF dff0(q, d, clk, reset); not n1(d, q); // not is a Verilog-provided primitive. case sensitive endmodule

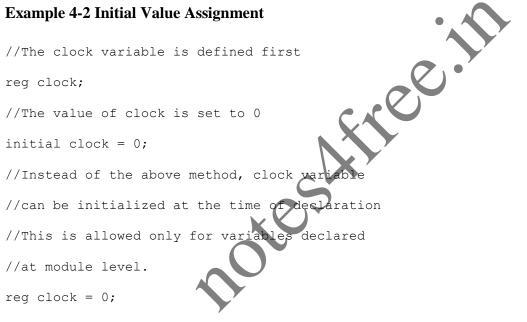

Since T\_FF instantiates D\_FF, we must now define (Example 1-5) the internals of module D\_FF. We assume asynchronous reset for the D\_FFF.

#### Example for Flipflop D\_F

| Example for Flipflop D_F                                                 |          |

|--------------------------------------------------------------------------|----------|

| // module D_FF with synchronous reset                                    |          |

| module D_FF(q, d, clk, reset);                                           | <b>Y</b> |

| output q;                                                                |          |

| input d, clk, reset;                                                     | -        |

| reg q;                                                                   |          |

| // Lots of new constructs. Ignore the functionality of the               |          |

| // constructs.                                                           |          |

| // Concentrate on how the design block is built in a top-down fashion. a | lways    |

| @(posedge reset or negedge clk)                                          |          |

| if (reset)                                                               |          |

| q <= 1'b0;                                                               |          |

| else                                                                     |          |

| $q \leq d;$                                                              |          |

endmodule

All modules have been defined down to the lowest-level leaf cells in the design methodology. The design block is now complete.

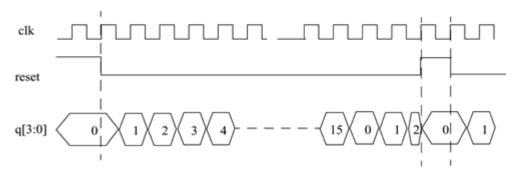

#### **1.21.2 Stimulus Block**

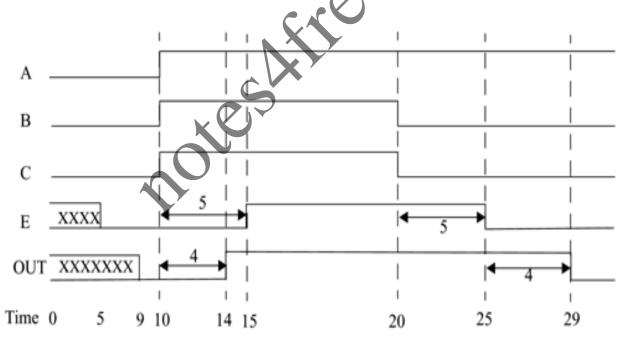

We need to write the stimulus block to check if the ripple carry counter design is functioning correctly. In this case, we must control the signals clk and reset so that the regular function of the ripple carry counter and the asynchronous reset mechanism are both tested. Consider the waveforms shown in Figure 1-9 to test the design. Waveforms for clk, reset, and 4-bit output q are shown. The cycle time for clk is 10 units; the

reset signal stays up from time 0 to 15 and then goes up again from time 195 to 205. Output q counts from 0 to 15.

Figure 1.9: Stimulus and Output Waveforms

#### **Example 1-6 Stimulus Block**

module stimulus; reg clk; ee. reg reset; wire[3:0] q; // instantiate the design block ripple\_carry\_counter r1(q, clk, reset); // Control the clk signal that drives the design block. Cycle time = 10initial clk = 1b0; //set clk to 0 always #5 clk = ~clk; //toggle clk every 5 time units// Control the reset signal that drives the design block // reset is asserted from 0 to 20 and from 200 to 220. initial begin reset = 1'b1; #15 reset = 1'b0;#180 reset = 1'b1;#10 reset = 1'b0;#20 \$finish; //terminate the simulation end // Monitor the outputs initial monitor( time, " Output q = % d", q);

endmodule

Once the stimulus block is completed, we are ready to run the simulation and verify the functional correctness of the design block.

The output obtained when stimulus and design blocks are simulated is shown in Example 1-7.

## Example for an Output of the Simulation

0 Output q = 020 Output q = 130 Output q = 240 Output q = 350 Output q = 460 Output q = 570 Output q = 680 Output q = 790 Output q = 8100 Output q = 9110 Output q = 10120 Output q = 11130 Output q = 12140 Output q = 13150 Output q = 14160 Output q = 15170 Output q = 0180 Output q = 1190 Output q = 2195 Output q = 0210 Output q = 1220 Output q = 2

| hotesti |

|---------|

|---------|

# 1.22: Outcomes

After completion of the module the students are able to:

- > Understand the importance, trends of HDL and design flow and design methodologies for digital design.

- > Differentiate the modules and module instances in Verilog with an example.

- Define stimulus block and design block

# **1.23: Recommended questions**

- 1. Discuss in brief about the evolution of CAD tools and HDLs used in digital system design.

- 2. Explain the typical VLSI IC design flow with the help of flow chart.

- 3. Discuss the trends in HDLs?

- 4. Why Verilog HDL has evolved as popular HDL in digital circuit design?

- 5. Explain the advantages of using HDLs over traditional schematic based design.

- 6. Describe the digital system design using hierarchical design methodologies with an example.

- 7. Apply the top-down design methodology to demonstrate the design of ripple carry counter.

- 8. Apply the bottom-up design methodology to demonstrate the design of 4-bit ripple carry adder.

- 9. Write Verilog HDL program to describe the 4-bit ripple carry counter.

- 10. Define Module and an Instance. Describe 4 different description styles of Verilog HDL.

- 11. Differentiate simulation and synthesis What is stimulus?

- 12. Write test bench to test the 4-bit ripple carry counter.

- 13. Write a test bench to test the 4-bit ripple carry adder.

# MODULE-2

# **BASIC CONCEPTS AND MODULES AND PORTS**

# **2.1: Objectives**

- > Understand the lexical conventions and define the logic value set and data type.

- > Identify useful system tasks and basic compiler directives.

- > Identify and understanding of components of a Verilog module definition.

- > Understand the port connection rules and connection to external signals by ordered list and by name.

# 2.2 Lexical conventions

The basic lexical conventions used by Verilog HDL are similar to those in the C programming language. Verilog contains a stream of tokens. Tokens can be comments, delimiters, numbers, strings, identifiers, and keywords. Verilog HDL is a case-sensitive language. All keywords are in lowercase.

## 2.2.1 Whitespace

Blank spaces (\b), tabs (\t) and newlines (\n) comprise the whitespace. Whitespace is ignored by Verilog except when it separates tokens. Whitespace is not ignored in strings.

# 2.2.2 Comments

Comments can be inserted in the code for readability and documentation. There are two ways to write comments. A one-line comment starts with "//". Verilog skips from that point to the end of line. A multiple-line comment starts with "/\*" and ends with "\*/". Multiple-line comments cannot be nested. However, one-line comments can be embedded in multiple-line comments.

a = b && c; // This is a one-line comment

/\* This is a multiple line comment

```

*/

```

/\* This is /\* an illegal \*/ comment \*/

/\* This is //a legal comment \*/

# 2.2.3 Operators

Operators are of three types: unary, binary, and ternary. Unary operators precede the operand. Binary operators appear between two operands. Ternary operators have two separate operators that separate three operands.

$a = \sim b$ ; // ~ is a unary operator. b is the operand

a = b && c; // && is a binary operator. b and c are operands

a = b? c : d; //?: is a ternary operator. b, c and d are operands

## 2.2.4 Number Specification

There are two types of number specification in Verilog: sized and unsized.

#### Sized numbers

Sized numbers are represented as <size> '<base format> <number>.

<size> is written only in decimal and specifies the number of bits in the number. Legal base formats are decimal ('d or 'D), hexadecimal ('h or 'H), binary ('b or 'B) and octal ('o or 'O). The number is specified as consecutive digits from 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, a, b, c, d, e, f. Only a subset of these digits is legal for a particular base. Uppercase letters are legal for number specification.

4'b1111 // This is a 4-bit binary number

12'habc // This is a 12-bit hexadecimal number

16'd255 // This is a 16-bit decimal number

#### **Unsized numbers**

Numbers that are specified without a <br/>base format> specification are decimal numbers by default. Numbers that are written without a <size> specification have a default number of bits that is simulator- and machine-specific (must be at least 32).

23456 // This is a 32-bit decimal number by default

'hc3 // This is a 32-bit hexadecimal number

'o21 // This is a 32-bit octal number

#### X or Z values

Verilog has two symbols for unknown and high impedance values. These values are very important for modeling real circuits. An unknown value is denoted by an x. A high impedance value is denoted by z.

12'h13x // This is a 12-bit hex number; 4 least significant bits unknown

- 6'hx // This is a 6-bit hex number

- 32'bz // This is a 32-bit high impedance number

An x or z sets four bits for a number in the hexadecimal base, three bits for a number in the octal base and one bit for a number in the binary base. If the most significant bit of a number is 0, x, or z, the number is automatically extended to fill the most significant bits, respectively, with 0, x, or z.

This makes it easy to assign x or z to whole vector. If the most significant digit is 1, then it is also zero extended.

#### **Negative numbers**

Negative numbers can be specified by putting a minus sign before the size for a constant number. Size constants are always positive. It is illegal to have a minus sign between <br/>base format> and <number>. An optional signed specifier can be added for signed arithmetic.

6'd3 // 8-bit negative number stored as 2's complement of 3

-6'sd3 // Used for performing signed integer math

4'd-2 // Illegal specification

## Underscore characters and question mark

An underscore character "\_" is allowed anywhere in a number except the first character. Underscore characters are allowed only to improve readability of numbers and are ignored by Verilog. A question mark "?" is the Verilog HDL alternative for z in the context of numbers. The ? is used to enhance readability in the casex and casez statements.

# 2.2.5 Strings

A string is a sequence of characters that are enclosed by double quotes. The restriction on a string is that it must be contained on a single line, that is, without a carriage return. It cannot be on multiple lines. Strings are treated as a sequence of one-byte ASCII values.

"Hello Verilog World" // is a string

"a / b" // is a string

# 2.2.6 Identifiers and Keywords

Keywords are special identifiers reserved to define the language constructs. Keywords are in lowercase. Identifiers are names given to objects so that they can be referenced in the design. Identifiers are made up of alphanumeric characters, the underscore ( $_$ ), or the dollar sign ( ). Identifiers are case sensitive. Identifiers start with an alphabetic character or an underscore. They cannot start with a digit or a \$ sign (The \$ sign as the first character is reserved for system tasks)

reg value; // reg is a keyword; value is an identifier

input clk; // input is a keyword, clk is an identifier

# **2.2.7 Escaped Identifiers**

Escaped identifiers begin with the backslash ( \ ) character and end with whitespace (space, tab, or newline). All characters between backslash and whitespace are processed literally. Any printable ASCII character can be included in escaped identifiers.

Neither the backslash nor the terminating whitespace is considered to be a part of the identifier.

a+b-c

\\*\*my\_name\*\*

# 2.3 Data Types

This section discusses the data types used in Verilog.

# 2.3.1 Value Set

Verilog supports four values and eight strengths to model the functionality of real hardware. The four value levels are listed in Table 2-1.

| Value Level | Condition in Hardware Circuits |

|-------------|--------------------------------|

| 0           | Logic zero, false condition    |

| 1           | Logic one, true condition      |

| x           | Unknown logic value            |

| Z           | High impedance, floating state |

Table 2-1. Value Levels

In addition to logic values, strength levels are often used to resolve conflicts between drivers of different strengths in digital circuits. Value levels 0 and 1 can have the strength levels listed in Table2-2.

| Strength Level | Туре           | Degree    |

|----------------|----------------|-----------|

| supply         | Driving        | strongest |

| strong         | Driving        |           |

| pull           | riving         | •         |

| large          | Storage        |           |

| weak           | Driving        |           |

| medium         | Storage        |           |

| small          | Storage        |           |

| highz          | High Impedance | weakest   |

Table 2-2. Strength Levels

If two signals of unequal strengths are driven on a wire, the stronger signal prevails. For example, if two signals of strength strong1 and weak0 contend, the result is resolved as a strong1. If two signals of equal strengths are driven on a wire, the result is unknown. If two signals of strength strong1 and strong0 conflict, the result is an x.

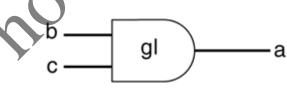

# 2.3.2 Nets

Nets represent connections between hardware elements. Just as in real circuits, nets have values continuously driven on them by the outputs of devices that they are connected to. In Figure 2.1 net a is connected to the output of and gate g1. Net a will continuously assume the value computed at the output of gate g1, which is b & c.

Figure 2.1. Example of Nets

Nets are declared primarily with the keyword wire. Nets are one-bit values by default unless they are declared explicitly as vectors. The terms wire and net are often used interchangeably. The default value of a net is z (except the trireg net, which defaults to x ). Nets get the output value of their drivers.

If a net has no driver, it gets the value z.

wire a; // Declare net a for the above circuit

wire b,c; // Declare two wires b,c for the above circuit

wire d = 1'b0; // Net d is fixed to logic value 0 at declaration.

## **2.3.3 Registers**

Registers represent data storage elements. Registers retain value until another value is placed onto them. In Verilog, the term register merely means a variable that can hold a value. Unlike a net, a register does not need a driver. Verilog registers do not need a clock as hardware registers do. Values of registers can be changed anytime in a simulation by assigning a new value to the register.

Register data types are commonly declared by the keyword reg.

## **Example 3-1 Example of Register**

reg reset; // declare a variable reset that can hold its value

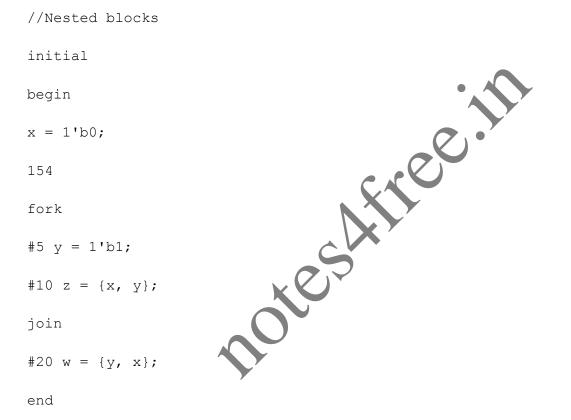

initial // keyword to specify the initial value of reg.

reset = 1'b1; //initialize reset to 1 to reset the digital circuit.

#100 reset = 1'b0; // after 100 time units reset is deasserted.Areel

end

## **Example 2-2 Signed Register Declaration**

reg signed [63:0] m; // 64 bit signed value integer i; // 32 bit signed value

# 2.3.4 Vectors

Nets or reg data types can be declared as vectors (multiple bit widths). If bit width is not specified, the default is scalar (1-bit).

wire a; // scalar net variable, default

wire [7:0] bus; // 8-bit bus

wire [31:0] busA,busB,busC; // 3 buses of 32-bit width.

reg clock; // scalar register, default

reg [0:40] virtual\_addr; // Vector register, virtual address 41 bits wide

Vectors can be declared at [high#: low#] or [low#: high#], but the left number in the squared brackets is always the most significant bit of the vector. In the example shown above, bit 0 is the most significant bit of vector virtual\_addr.

## **Vector Part Select**

For the vector declarations shown above, it is possible to address bits or parts of vectors.

busA[7] // bit # 7 of vector busA

bus[2:0] // Three least significant bits of vector bus,

// using bus[0:2] is illegal because the significant bit shouldalways be on the left of a range specification virtual addr[0:1] // Two most significant bits of vector virtual addr

## Variable Vector Part Select

Another ability provided in Verilog HDL is to have variable part selects of a vector. This allows part selects to be put in for loops to select various parts of the vector. There are two special part-select operators:

[*<starting\_bit>+:width*] - part-select increments from starting bit.

[*<starting\_bit>-:width*] - part-select decrements from starting bit.

The starting bit of the part select can be varied, but the width has to be constant. The following example iree. shows the use of variable vector part select:

reg [255:0] data1; //Little endian notation

reg [0:255] data2; //Big endian notation

reg [7:0] byte;

//Using a variable part select, one can choose part

byte = data1[31-:8]; //starting bit = 31, width  $-8 \rightarrow$  data[31:24]

byte = data1[24+:8]; //starting bit = 24, width = 8 => data[31:24]

byte = data2[31-:8]; //starting bit =  $\beta$ 1, width =8 => data[24:31]

byte = data2[24+:8]; //starting bit = 24, width = 8 => data[24:31]

//The starting bit can also be a variable. The width has to be constant.

//Therefore, one can use the variable part select

//in a loop to select all bytes of the vector.

for (j=0; j<=31; j=j+1)

byte = data1[(j\*8)+:8]; //Sequence is [7:0], [15:8]... [255:248]

//Can initialize a part of the vector

data1[(byteNum\*8)+:8] = 8'b0; //If byteNum = 1, clear 8 bits [15:8]

# 2.3.5 Integer, Real, and Time Register Data Types

Integer, real, and time register data types are supported in Verilog.

#### Integer

An integer is a general purpose register data type used for manipulating quantities. Integers are declared by the keyword integer. Although it is possible to use reg as a general-purpose variable, it is more convenient to declare an integer variable for purposes such as counting. The default width for an integer is the hostmachine word size, which is implementation-specific but is at least 32 bits. Registers declared as data type reg store values as unsigned quantities, whereas integers store values as signed quantities.

integer counter; // general purpose variable used as a counter.

initial

counter = -1; // A negative one is stored in the counter

## Real

Real number constants and real register data types are declared with the keyword real. They can be specified in decimal notation (e.g., 3.14) or in scientific notation (e.g., 3e6, which is  $3 \times 10^6$ ). Real numbers cannot have a range declaration, and their default value is 0. When a real value is assigned to an integer, the real number is rounded off to the nearest integer.

real delta; // Define a real variable called delta initial

begin

delta = 4e10; // delta is assigned in scientific notation

delta = 2.13; // delta is assigned a value 2.13 end

integer i; // Define an integer i

initial

i = delta; // i gets the value 2 (rounded value of 2.13)

## Time

Verilog simulation is done with respect to simulation time. A special time register data type is used in Verilog to store simulation time. A time variable is declared with the keyword time. The width for time register data types is implementation-specific but is at least 64 bits. The system function \$time is invoked to get the current simulation time.

time save\_sim\_time; // Define a time variable save\_sim\_time

initial

save\_sim\_time = \$time; // Save the current simulation time

#### Arrays

Arrays are allowed in Verilog for reg, integer, time, real, realtime and vector register data types. Multidimensional arrays can also be declared with any number of dimensions. Arrays of nets can also be used to connect ports of generated instances. Each element of the array can be used in the same fashion as a scalar or vector net. Arrays are accessed by <array\_name>[<subscript>]. For multi- dimensional arrays, indexes need to be provided for each dimension.

integer count[0:7]; // An array of 8 count variables

reg bool[31:0]; // Array of 32 one-bit boolean register variables time

chk\_point[1:100]; // Array of 100 time checkpoint variables reg [4:0]

port\_id[0:7]; // Array of 8 port\_ids; each port\_id is 5 bits wide

integer matrix[4:0][0:255]; // Two dimensional array of integers

reg [63:0] array\_4d [15:0][7:0][7:0][255:0]; //Four dimensional array

wire [7:0] w\_array2 [5:0]; // Declare an array of 8 bit vector wire

wire w\_array1[7:0][5:0]; // Declare an array of single bit wires.

It is important not to confuse arrays with net or register vectors. A vector is a single element that is n-bits wide. On the other hand, arrays are multiple elements that are 1-bit or n-bits wide.

Examples of assignments to elements of arrays discussed above are shown below:

count[5] = 0; // Reset 5th element of array of count variables

chk\_point[100] = 0; // Reset 100th time check point value

port\_id[3] = 0; // Reset 3rd element (a 5-bit value) of port\_id array.

matrix[1][0] = 33559; // Set value of element indexed by [1][0] to 33559

port\_id = 0; // Illegal syntax - Attempt to write the entire array

matrix [1] = 0; // Illegal syntax - Attempt to write [1][0]..[1][255]

# 2.3.6 Memories

In digital simulation, one often needs to model register files, RAMs, and ROMs. Memories are modeled in Verilog simply as a one-dimensional array of registers. Each element of the array is known as an element or word and is addressed by a single array index. Each word can be one or more bits. It is important to differentiate between n 1-bit registers and one n-bit register. A particular word in memory is obtained by using the address as a memory array subscript.

reg mem1bit[0:1023]; // Memory mem1bit with 1K 1-bit words reg [7:0] membyte[0:1023]; // Memory membyte with 1K 8-bit words(bytes) membyte[511] // Fetches 1 byte word whose address is 511.

# 2.3.7 Parameters

Verilog allows constants to be defined in a module by the keyword parameter. Parameters cannot be used as variables. Parameter values for each module instance can be overridden individually at compile time. This allows the module instances to be customized. This aspect is discussed later. Parameter types and sizes can also be defined.

parameter port\_id = 5; // Defines a constant port\_id

parameter cache\_line\_width = 256; // Constant defines width of cache line

parameter signed [15:0] WIDTH; // Fixed sign and range for parameter WIDTH

## 2.3.8 Strings

Strings can be stored in reg. The width of the register variables must be large enough to hold the string. Each character in the string takes up 8 bits (1 byte). If the width of the register is greater than the size of the string, Verilog fills bits to the left of the string with zeros. If the register width is smaller than the string width, Verilog truncates the leftmost bits of the string. It is always safe to declare a string that is slightly wider than necessary. reg [8\*18:1] string\_value; // Declare a variable that is 18 bytes wide initial string\_value = "Hello Verilog World"; // String can be stored in variable

Special characters serve a special purpose in displaying strings, such as newline, tabs, and displaying argument values. Special characters can be displayed in strings only when they are preceded by escape characters, as shown in Table 2-3

| Escaped Characters | Character Displayed                   |  |  |  |

|--------------------|---------------------------------------|--|--|--|

| \n                 | newline                               |  |  |  |

| \t                 | tab                                   |  |  |  |

| %%                 | %                                     |  |  |  |

| //                 | 1                                     |  |  |  |

| /"                 |                                       |  |  |  |

| \000               | Character written in 1?3 octal digits |  |  |  |

| Table 2-3. Special Character | S |

|------------------------------|---|

|------------------------------|---|

# 2.4 System Tasks and Compiler Directives

In this section, we introduce two special concepts used in Verilog: system tasks and compiler directives.

#### 2.4.1 System Tasks

Verilog provides standard system tasks for certain routine operations. All system tasks appear in the form \$<keyword>. Operations such as displaying on the screen, monitoring values of nets, stopping, and finishing are done by system tasks.

## **Displaying information**

\$display is the main system task for displaying values of variables or strings or expressions. This is one of the most useful tasks in Verilog.

Usage: \$display(p1, p2, p3,...., pn);

p1, p2, p3,..., pn can be quoted strings or variables or expressions. The format of \$display is very similar to printf in C. A \$display inserts a newline at the end of the string by default. A \$display without any arguments produces a newline.

## **Monitoring information**

Verilog provides a mechanism to monitor a signal when its value changes. This facility is provided by the \$monitor task.

Usage: \$monitor(p1,p2,p3,....,pn);

The parameters p1, p2, ..., pn can be variables, signal names, or quoted strings. A format similar to the \$display task is used in the \$monitor task. \$monitor continuously monitors the values of the variables or signals specified in the parameter list and displays all parameters in the list whenever the value of any one variable or signal changes. Unlike \$display, \$monitor needs to be invoked only once. Only one monitoring list can be active at a time.

If there is more than one \$monitor statement in your simulation, the last \$monitor statement will be the active statement. The earlier \$monitor statements will be overridden.

Two tasks are used to switch monitoring on and off.

Usage:

\$monitoron;

\$monitoroff;

The \$monitoron tasks enables monitoring, and the \$monitoroff task disables monitoring during a simulation.

#### **Example of Monitor Statement**

//Monitor time and value of the signals clock and reset

//Clock toggles every 5 time units and reset goes down at 10 time units

initial

begin

\$monitor (\$time," Value of signals clock = %b reset = %b", clock,reset);

end

Partial output of the monitor statement:

-- 0 Value of signals clock = 0 reset = 1

-- 5 Value of signals clock = 1 reset = 1

-- 10 Value of signals clock = 0 reset = 0

## Stopping and finishing in a simulation

The task \$stop is provided to stop during a simulation.

Usage: \$stop;

The \$stop task puts the simulation in an interactive mode. The designer can then debug the design from the interactive mode. The \$stop task is used whenever the designer wants to suspend the simulation and examine the values of signals in the design.

ee.

The \$finish task terminates the simulation.

Usage: \$finish;

Examples of \$stop and \$finish are given below

## **Example of Stop and Finish Tasks**

// Stop at time 100 in the simulation and examine the results

// Finish the simulation at time 1000.

initial

begin

clock = 0;

reset = 1;

#100 stop; // This will suspend the simulation at time = 100

#900 \$finish; // This will terminate the simulation at time = 1000

end

#### **2.4.2** Compiler Directives

Compiler directives are provided in Verilog. All compiler directives are defined by using the `<keyword> construct. The two most useful compiler directives are

#### `define

The `define directive is used to define text macros in Verilog .The Verilog compiler substitutes the text of the macro wherever it encounters a `<macro\_name>. This is similar to the #define construct in C. The defined constants or text macros are used in the Verilog code by preceding them with a ` (back tick).

#### **Example for `define Directive**

//define a text macro that defines default word size

//Used as 'WORD\_SIZE in the code

'define WORD\_SIZE 32

//define an alias. A \$stop will be substituted wherever 'S appears

'define S \$stop;

//define a frequently used text string

'define WORD\_REG reg [31:0]

#### `include

The `include directive allows you to include entire contents of a Verilog source file in another Verilog file during compilation. This works similarly to the #include in the C programming language.

,ee?

#### **Example for `include Directive**

// Include the file header.v, which contains declarations in themain verilog file design.v.

'include header.v

•••

<Verilog code in file design.v>

## **2.5 Modules**

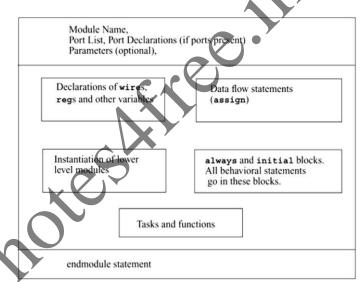

Module is a basic building block in Verilog. A module definition always begins with the keyword module. The module name, port list, port declarations, and optional parameters must come first in a module definition. Port list and port declarations are present only if the module has any ports to interact with the external environment.

The five components within a module are: variable declarations, dataflow statements, instantiation of lower modules, behavioral blocks, and tasks or functions. These components can be in any order and at any place in the module definition.

The endmodule statement must always come last in a module definition. All components except module, module name, and endmodule are optional and can be mixed and matched as per design needs. Verilog allows multiple modules to be defined in a single file. The modules can be defined in any order in the file.

Figure 2.2.:Components of a Verilog Module

Consider a simple example of an SR latch, as shown in Figure 2.3

The SR latch has S and R as the input ports and Q and Qbar as the output ports. The SR latch and its stimulus can be modeled as shown in Example.

#### **Example of Components of SR Latch**

// This example illustrates the different components of a module

// Module name and port list

// SR latch module

module SR\_latch(Q, Qbar, Sbar, Rbar);

//Port declarations

output Q, Qbar;

input Sbar, Rbar;

// Instantiate lower-level modules

// In this case, instantiate Verilog primitive nand gates

ION. NAL // Note how the wires are connected in a cross-coupled fashion. nand n1(Q, Sbar, Qbar);

nand n2(Qbar, Rbar, Q);

// endmodule statement

endmodule

// Module name and port list

// Stimulus module

module Top;

// Declarations of wire, reg, and other variables

reg set, reset;

// Instantiate lower-level modules

// In this case, instantiate SR\_latch Feed inverted set and reset signals to the SR latch

SR\_latch m1(q, qbar, ~set, ~reset);

// Behavioral block, initial

initial

begin

monitor( set = %b, reset= %b, q= %b\n", set, reset, q);

set = 0; reset = 0;

#5 reset = 1;

#5 reset = 0;

#5 set = 1;

end

// endmodule statement

#### endmodule

From the above example following characteristics are noticed:

• In the SR latch definition above ,all components described in Figure 2-2 need not be present in a module. We do not find variable declarations, dataflow (assign) statements, or behavioral blocks (always or initial).

• However, the stimulus block for the SR latch contains module name, wire, reg, and variable declarations, instantiation of lower level modules, behavioral block (initial), and endmodule statement but does not contain port list, port declarations, and data flow (assign) statements.

• Thus, all parts except module, module name, and endmodule are optional and can be mixed and matched as per design needs.

## 2.6 Ports

Ports provide the interface by which a module can communicate with its environment. For example, the input/output pins of an IC chip are its ports. The environment can interact with the module only through its ports. The internals of the module are not visible to the environment. This provides a very powerful flexibility to the designer. The internals of the module can be changed without affecting the environment as long as the interface is not modified. Ports are also referred to as terminals.

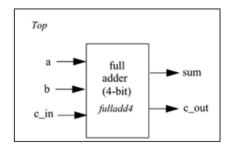

# 2.6.1 List of Ports

A module definition contains an optional list of ports. If the module does not exchange any signals with the environment, there are no ports in the list. Consider a 4-bit full adder that is instantiated inside a top-level module Top. The diagram for the input/output ports is shown in Figure 2-4.

Figure 2-4. I/O Ports for Top and Full Adder

From the above figure, the module Top is a top-level module. The module fulladd4 is instantiated below Top. The module fulladd4 takes input on ports a, b, and c\_in and produces an output on ports sum and c\_out. Thus, module fulladd4 performs an addition for its environment. The module Top is a top-level module in the simulation and does not need to pass signals to or receive signals from the environment. Thus, it does not have a list of ports. The module names and port lists for both module declarations in Verilog are as shown in below example.

#### **Example of List of Ports**

module fulladd4(sum, c\_out, a, b, c\_in); //Module with a list of ports module Top; // No list of ports, top-level module in simulation

#### **2.6.2** Port Declaration

All ports in the list of ports must be declared in the module. Ports can be declared as follows:

input -Input port

output- Output port

inout- Bidirectional port

Each port in the port list is defined as input, output, or inout, based on the direction of the port signal. Thus, for the example of the the port declarations will be as shown in example below.

#### **Example for Port Declarations**

module fulladd4(sum, c\_out, a, b, e\_//Begin port declarations section

output[3:0] sum;

output c\_cout;

input [3:0] a, b;

input c\_in;

//End port declarations section

•••

<module internals>

... endmodule

All port declarations are implicitly declared as wire in Verilog. Thus, if a port is intended to be a wire, it is sufficient to declare it as output, input, or inout. Input or inout ports are normally declared as wires.

However, if output ports hold their value, they must be declared as reg. Ports of the type input and inout cannot be declared as reg because reg variables store values and input ports should not store values but simply reflect the changes in the external signals they are connected to.

Alternate syntax for port declaration is shown in below example. This syntax avoids the duplication of naming the ports in both the module definition statement and the module port list definitions. If a port is declared but no data type is specified, then, under specific circumstances, the signal will default to a wire data type.

#### **Example for ANSI C Style Port Declaration Syntax**

```

module fulladd4(output reg [3:0] sum,

output reg c_out,

input [3:0] a, b, //wire by default

input c_in); //wire by default

...

```

<module internals>

```

•••

```

endmodule

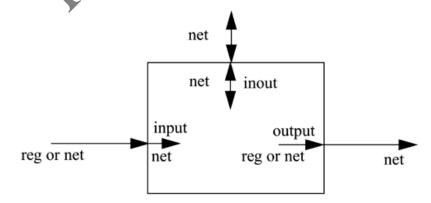

## 2.6.3 Port Connection Rules

A port as consisting of two units, one unit that is internal to the module and another that is external to the module. The internal and external units are connected. There are rules governing port connections when modules are instantiated within other modules. The Verilog simulator complains if any port connection rules are violated. These rules are summarized in Figure 2.5

Areel

Figure 2-5. Port Connection Rules

#### Inputs

Internally, input ports must always be of the type net. Externally, the inputs can be connected to a variable which is a reg or a net.

#### Outputs

Internally, outputs ports can be of the type reg or net. Externally, outputs must always be connected to a net. They cannot be connected to a reg.

## Inouts

Internally, inout ports must always be of the type net. Externally, inout ports must always be connected to a net.

#### Width matching

It is legal to connect internal and external items of different sizes when making intermodule port connections. However, a warning is typically issued that the widths do not match.

#### **Unconnected ports**

Verilog allows ports to remain unconnected. For example, certain output ports might be simply for debugging, and you might not be interested in connecting them to the external signals. You can let a port remain unconnected by instantiating a module as shown below

fulladd4 fa0 (SUM, , A, B, C\_IN), // Output port c\_out is unconnected

## Example of illegal port connection

To illustrate port connection rules, assume that the module fulladd4 Example is instantiated in the stimulus block Top. Below example shows an illegal port connection

## **Example 2-14 Illegal Port Connection**

module Top;

//Declare connection variables reg

[3:0]A,B;

reg C\_IN;

reg [3:0] SUM;

wire C\_OUT;

//Instantiate fulladd4, call it fa0

fulladd4 fa0(SUM, C\_OUT, A, B, C\_IN);

//Illegal connection because output port sum in module fulladd4

//is connected to a register variable SUM in module Top.

<stimulus>

. endmodule

This problem is rectified if the variable SUM is declared as a net (wire).

# 2.7 Connecting Ports to External Signals

There are two methods of making connections between signals specified in the module instantiation and the ports in a module definition. These two methods cannot be mixed. These methods are

#### Connecting by ordered list

The signals to be connected must appear in the module instantiation in the same order as the ports in the port list in the module definition. Consider the module fulladd4.To connect signals in module Top by ordered list, the Verilog code is shown in below example. Notice that the external signals SUM, C\_OUT, A, B, and C\_IN appear in exactly the same order as the ports sum, c\_out, a, b, and c\_in h module definition of fulladd4.

# otesk **Example 2-15 Connection by Ordered List**

module Top;

//Declare connection variables

reg [3:0]A,B;

reg C\_IN;

wire [3:0] SUM;

wire C\_OUT;

//Instantiate fulladd4, call it fa\_ordered.

//Signals are connected to ports in order (by position)

fulladd4 fa\_ordered (SUM, C\_OUT, A, B, C\_IN);

...

<stimulus>

... endmodule

module fulladd4(sum, c\_out, a, b, c\_in);

output[3:0] sum; output c\_cout; input [3:0] a, b; input c\_in;

•••

<module internals>

... endmodule

## **Connecting ports by name**

For large designs where modules have, say, 50 ports, remembering the order of the ports in the module definition is impractical and error-prone. Verilog provides the capability to connect external signals to ports by the port names, rather than by position. We could connect the ports by name in above example by instantiating the module fulladd4, as follows. Note that you can specify the port connections in any order as long as the port name in the module definition correctly matches the external signal.

// Instantiate module fa\_byname and connect signals to ports by name

fulladd4 fa\_byname(.c\_out(C\_OUT), .sum(SUM), .b(B), .c\_in(C\_IN), .a(A),);

Note that only those ports that are to be connected to external signals must be specified in port connection by name. Unconnected ports can be dropped. For example, if the port c\_out were to be kept unconnected, the instantiation of fulladd4 would look as follows. The port c\_out is simply dropped from the port list.

// Instantiate module fa\_byname and connect signals to ports by

name fulladd4 fa\_byname(.sum(SUM), .b(B), .c\_in(C\_IN), .a(A),);

Another advantage of connecting ports by name is that as long as the port name is not changed, the order of ports in the port list of a module can be rearranged without changing the port connections in module instantiations.

# **2.8 Hierarchical Names**

Every module instance, signal, or variable is defined with an identifier. A particular identifier has a unique place in the design hierarchy. Hierarchical name referencing allows us to denote every identifier in the design hierarchy with a unique name. A hierarchical name is a list of identifiers separated by dots (".") for each level of hierarchy. Thus, any identifier can be addressed from any place in the design by simply specifying the complete hierarchical name of that identifier. The top-level module is called the root module because it is not instantiated anywhere. It is the starting point.

To assign a unique name to an identifier, start from the top-level module and trace the path along the design hierarchy to the desired identifier.

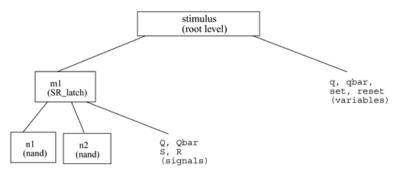

Consider the simulation of SR latch Example. The design hierarchy is shown in Figure 2.6.

Figure 2-6. Design Hierarchy for SR Latch Simulation

For this simulation, stimulus is the top-level module. Since the top-level module is not instantiated anywhere, it is called the root module. The identifiers defined in this module are q, gbar, set, and reset. The root module instantiates m1, which is a module of type SR\_latch. The module m1 instantiates nand gates n1 and n2. Q, Qbar, S, and R are port signals in instance m1. Hierarchical name referencing assigns a unique name to each identifier. To assign hierarchical names, use the module name for root module and instance names for all module instances below the root module. notes

Example stimulus stimulus.q stimulus.qbar timulus.set stimulus.reset stimulus.m1 stimulus.m1.Q stimulus.m1.Qbar stimulus m1.S stimulus.m1.R stimulus.n1 stimulus.n2

Each identifier in the design is uniquely specified by its hierarchical path name. To display the level of hierarchy, use the special character %m in the \$display task.

# 2.9: Outcomes

After completion of the module the students are able to:

- > Understand the lexical conventions and different data types of verilog.

- ➢ Identify useful system tasks such as \$display and \$monitor and basic compiler directives.

- > Understand different components of a Verilog module definition

- Understand the port connection rules and connection to external signals by ordered list and by name

# 2.10: Recommended questions

- 1. Describe the lexical conventions used in Verilog HDL with examples.

- 2. Explain different data types of Verilog HDL with examples

- 3. What are system tasks and compiler directives?

- 4. What are the uses of \$monitor, \$display and \$finish system tasks? Explain with examples.

- 5. Explain `define and `include compiler directives.

- 6. Explain the components of Verilog HDL module.

- 7. What are the components of SR latch? Write Verilog HDL module of SR latch.

- 8. Explain the different types of ports supported by Verilog HDL with examples.

- 9. Explain the port connection rules of Verilog HDL with examples.

- 10. How hierarchical names helps in addressing any identifier used in the design from any other level of hierarchy? Explain with examples.

- 11. What are the basic components of a module? Which components are mandatory?

# **MODULE -3**

# GATE LEVEL MODELING AND DATA FLOW MODELING

## 3.1: Objectives

- > Identify logic gate primitives provided in Verilog.

- > Understand instantiation of gates, gate symbols, and truth tables for and/or and buf/not type gates.

- > Understand how to construct a Verilog description from the logic diagram of the circuit.

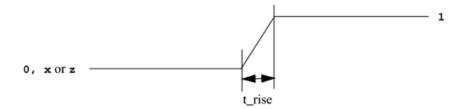

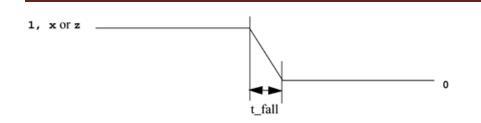

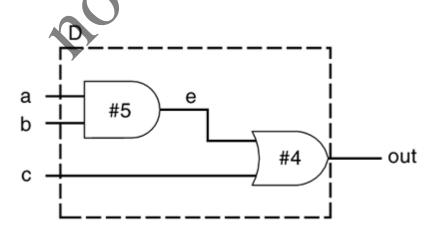

- Describe rise, fall, and turn-off delays in the gate-level design and Explain min, max, and typ delays in the gate-level design

- Describe the continuous assignment (assign) statement, restrictions on the assign statement, and the implicit continuous assignment statement.

- Explain assignment delay, implicit assignment delay, and net declaration delay for continuous assignment statements and Define expressions, operators, and operands.

- > Use dataflow constructs to model practical digital circuits in Verilog

# **3.2 Gate Types**

A logic circuit can be designed by use of logic gates. Verilog supports basic logic gates as predefined primitives. These primitives are instantiated like modules except that they are predefined in Verilog and do not need a module definition. All logic circuits can be designed by using basic gates. There are two classes of basic gates: and/or gates and buf/not gates.

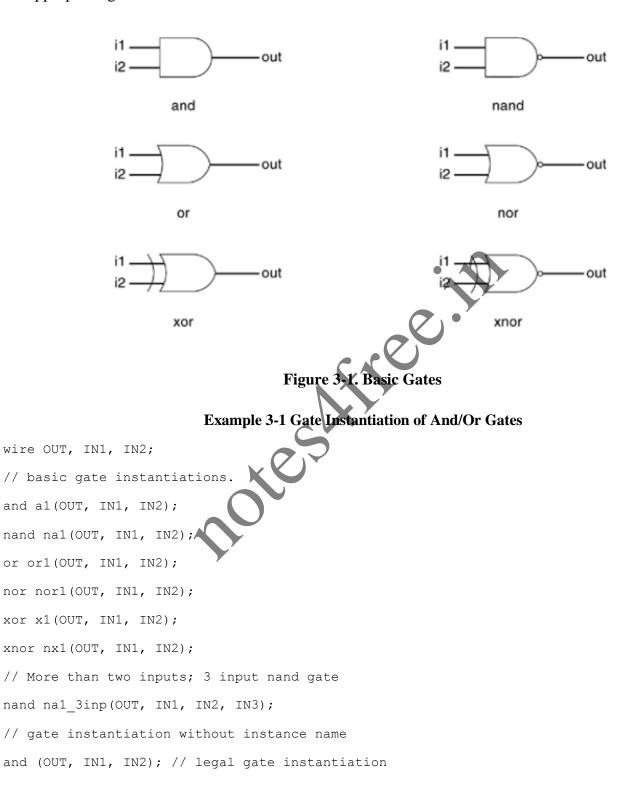

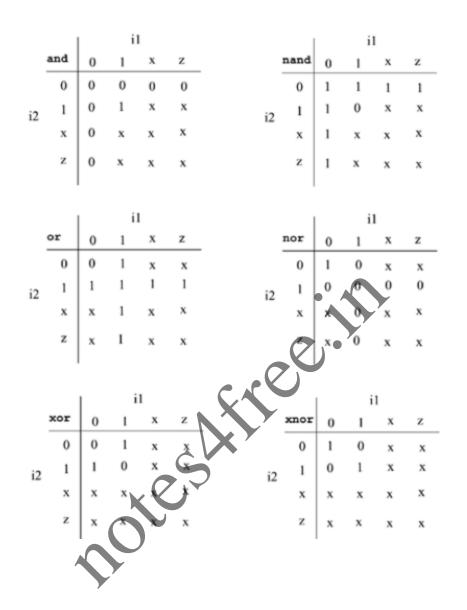

## 3.2.1 And/Or Gates

And/or gates have one scalar output and multiple scalar inputs. The first terminal in the list of gate terminals is an output and the other terminals are inputs. The output of a gate is evaluated as soon as one of the inputs changes. The and/or gates available in Verilog are: **and, or, xor, nand, nor, xnor.**

The corresponding logic symbols for these gates are shown in Figure 3-1. Consider the gates with two inputs. The output terminal is denoted by out. Input terminals are denoted by i1 and i2.

These gates are instantiated to build logic circuits in Verilog. Examples of gate instantiations are shown below. In Example 3-1, for all instances, OUT is connected to the output out, and IN1 and IN2 are connected to the two inputs i1 and i2 of the gate primitives. Note that the instance name does not need to be specified for primitives. This lets the designer instantiate hundreds of gates without giving them a name. More than two inputs can be specified in a gate instantiation. Gates with more than two inputs are

instantiated by simply adding more input ports in the gate instantiation. Verilog automatically instantiates the appropriate gate.

The truth tables for these gates define how outputs for the gates are computed from the inputs. Truth tables are defined assuming two inputs. The truth tables for these gates are shown in Table 3-1. Outputs of gates with more than two inputs are computed by applying the truth table iteratively.

Dept.of ECE/ATMECE, Mysuru

## Table 3-1. Truth Tables for And/Or

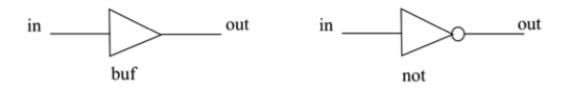

## 3.2.2 Buf/Not Gates

Buf/not gates have one scalar input and one or more scalar outputs. The last terminal in the port list is connected to the input. Other terminals are connected to the outputs. We will discuss gates that have one input and one output. Two basic buf/not gate primitives are provided in Verilog

## buf not

The symbols for these logic gates are shown in Figure 3-2.

Figure 3-2. Buf/not Gates

These gates are instantiated in Verilog as shown Example 3-2. Notice that these gates can have multiple outputs but exactly one input, which is the last terminal in the port list.

## **Example 3-2 Gate Instantiations of Buf/Not Gates**

| // basic gate instantiations.                                                |    |     |  |     |    |     |  |  |  |  |

|------------------------------------------------------------------------------|----|-----|--|-----|----|-----|--|--|--|--|

| buf b1(OUT1, IN);                                                            |    |     |  |     |    |     |  |  |  |  |

| not n1(OUT1, IN);                                                            |    |     |  |     |    |     |  |  |  |  |

| // More than two outputs                                                     |    |     |  |     |    |     |  |  |  |  |

| <pre>buf b1_2out(OUT1, OUT2, IN);</pre>                                      |    |     |  |     |    |     |  |  |  |  |

| // gate instantiation without instance name                                  |    |     |  |     |    |     |  |  |  |  |

| not (OUT1, IN); // legal gate instantiation                                  |    |     |  |     |    |     |  |  |  |  |

| Truth tables for gates with one input and one output are shown in Table 3-2. |    |     |  |     |    |     |  |  |  |  |

| Table 3-2. Truth Tables for Buf/Not Gates                                    |    |     |  |     |    |     |  |  |  |  |

|                                                                              |    |     |  |     |    |     |  |  |  |  |

| buf                                                                          | in | out |  | not | in | out |  |  |  |  |

|                                                                              | 0  | 0   |  |     | 0  | 1   |  |  |  |  |

|                                                                              | 1  | 1   |  |     | 1  | 0   |  |  |  |  |

|                                                                              | x  | x   |  |     | x  | x   |  |  |  |  |

|                                                                              | z  | x   |  |     | z  | x   |  |  |  |  |

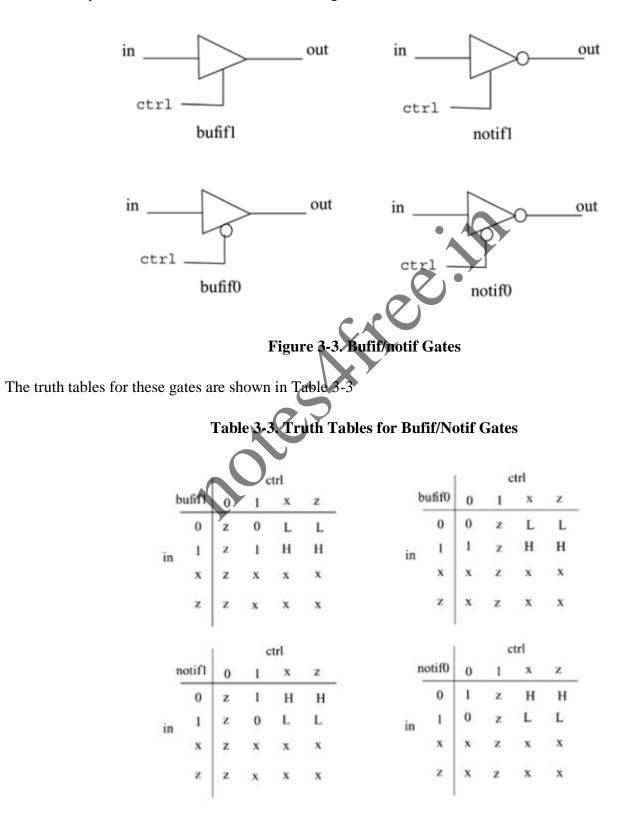

## **Bufif/notif**

Gates with an additional control signal on buf and not gates are also available.

bufif1 notif1

## bufif0 notif0

These gates propagate only if their control signal is asserted. They propagate z if their control signal is deasserted. Symbols for bufif/notif are shown in Figure 3-3.

These gates are used when a signal is to be driven only when the control signal is asserted. Such a situation is applicable when multiple drivers drive the signal. These drivers are designed to drive the signal on mutually exclusive control signals. Example 3-3 shows examples of instantiation of bufif and notif gates.

### **Example 3-3 Gate Instantiations of Bufif/Notif Gates**

//Instantiation of bufif gates.

bufif1 b1 (out, in, ctrl);

bufif0 b0 (out, in, ctrl);

//Instantiation of notif gates

notif1 n1 (out, in, ctrl);

notif0 n0 (out, in, ctrl);

## **3.2.3 Array of Instances**

There are many situations when repetitive instances are required. These instances differ from each other only by the index of the vector to which they are connected. To simplify specification of such instances, Verilog HDL allows an array of primitive instances to be defined. Example3-4 shows an example of an array of instances.

## **Example 3-4 Simple Array of Primitive Instances**

```

wire [7:0] OUT, IN1, IN2;

// basic gate instantiations.

nand n_gate[7:0] (OUT, IN1, IN2);

// This is equivalent to the following 8 instantiations

nand n_gate0 (OUT[0], IN1[0], IN2[0]);

nand n_gate1 (OUT[1], IN1[1], IN2[1]);

nand n_gate2 (OUT[2], IN1[2], IN2[2]);

nand n_gate3 (OUT[3], IN1[3], IN2[3]);

nand n_gate4 (OUT[4], IN1[4], IN2[4]);

nand n_gate5 (OUT[5], IN1[5], IN2[5]);

nand n_gate6 (OUT[6], IN1[6], IN2[6]);

```

```

nand n gate7(OUT[7], IN1[7], IN2[7]);

```

## 3.1.4 Examples

Having understood the various types of gates available in Verilog, consider the real examples that illustrates design of gate-level digital circuits.

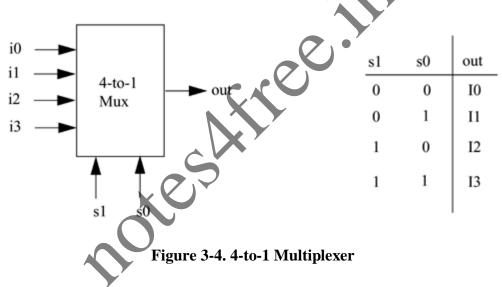

## **Gate-level multiplexer**

Consider the design of 4-to-1 multiplexer with 2 select signals. Multiplexers serve a useful purpose in logic design. They can connect two or more sources to a single destination. They can also be used to implement Boolean functions. We will assume for this example that signals s1 and s0 do not get the value x or z. The I/O diagram and the truth table for the multiplexer are shown in Figure 3-4. The I/O diagram will be useful in setting up the port list for the multiplexer.

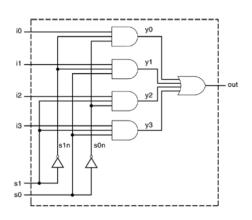

Implement the logic for the multiplexer using basic logic gates. The logic diagram for the multiplexer is shown in Figure 3-5.

Figure 3-5. Logic Diagram for Multiplexer

The logic diagram has a one-to-one correspondence with the Verilog description. The Verilog description for the multiplexer is shown in Example 3-5. Two intermediate nets, s0n and s1n, are created; they are complements of input signals s1 and s0. Internal nets y0, y1, y2, y3 are also required. Note that instance names are not specified for primitive gates, not, and, and or. Instance names are optional for Verilog primitives but are mandatory for instances of user-defined modules.

## **Example 3-5 Verilog Description of Multiplexer**

```

// Module 4-to-1 multiplexer. Port list is taken exactly from

// the I/O diagram.

module mux4 to 1 (out, i0, i1, i2, i3, s1, s0);

oteshin

// Port declarations from the I/O diagram

output out;

input i0, i1, i2, i3;

input s1, s0;

// Internal wire declarations

wire s1n, s0n;

wire y0, y1, y2, y3;

// Gate instantiations

// Create s1n and s0n sign

not (s1n, s1);

not (s0n, s0);

// 3-input and gates instantiated

and (y0, i0, s1n, s0n);

and (y1, i1, s1n, s0);

and (y2, i2, s1, s0n);

and (y3, i3, s1, s0);

// 4-input or gate instantiated

or (out, y0, y1, y2, y3);

```

endmodule

This multiplexer can be tested with the stimulus shown in Example 3-6. The stimulus checks that each combination of select signals connects the appropriate input to the output. The signal OUTPUT is displayed one time unit after it changes. System task \$monitor could also be used to display the signals when they change values.

### **Example 3-6 Stimulus for Multiplexer**

```

// Define the stimulus module (no ports)

module stimulus;

// Declare variables to be connected

skieen

// to inputs

reg INO, IN1, IN2, IN3;

reg S1, S0;

// Declare output wire

wire OUTPUT;

// Instantiate the multiplexer

mux4 to 1 mymux(OUTPUT, INO, IN1)

IN3, S1, S0);

// Stimulate the inputs

// Define the stimulus module

(no ports)

initial

begin

// set input lines

INO = 1; IN1 = 0; IN2 = 1; IN3 = 0;

#1 $display("IN0= %b, IN1= %b, IN2= %b, IN3= %b\n",IN0,IN1,IN2,IN3);

// choose INO

S1 = 0; S0 = 0;

#1 $display("S1 = %b, S0 = %b, OUTPUT = %b \n", S1, S0, OUTPUT);

// choose IN1

```

```

S1 = 0; S0 = 1;

#1 $display("S1 = %b, S0 = %b, OUTPUT = %b \n", S1, S0, OUTPUT);

// choose IN2

S1 = 1; S0 = 0;

#1 $display("S1 = %b, S0 = %b, OUTPUT = %b \n", S1, S0, OUTPUT);

// choose IN3

S1 = 1; S0 = 1;

#1 display("S1 = b, S0 = b, OUTPUT = b \n", S1, S0, OUTPUT);

end

endmodule

The output of the simulation is shown below. Each combination of the select signals is tested.

INO= 1, IN1= 0, IN2= 1, IN3= 0

S1 = 0, S0 = 0, OUTPUT = 1

S1 = 0, S0 = 1, OUTPUT = 0

S1 = 1, S0 = 0, OUTPUT = 1

S1 = 1, S0 = 1, OUTPUT = 0

```

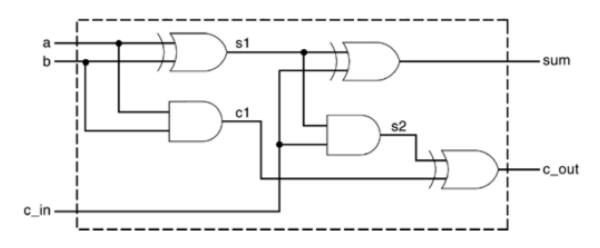

## 4-bit Ripple Carry Full Adder

Consider the design of a 4-bit full adder whose port list was defined in, List of Ports. We use primitive logic gates, and we apply stimulus to the 4-bit full adder to check functionality. For the sake of simplicity, we will implement a ripple carry adder. The basic building block is a 1-bit full adder. The mathematical equations for a 1-bit full adder are shown below.

sum = (a b cin)

cout = (a b) + cin (a b)

The logic diagram for a 1-bit full adder is shown in Figure 3-6.

Figure 3-6. 1-bit Full Adder

This logic diagram for the 1-bit full adder is converted to a Verilog description, shown in Example 3-7.

| Example 3-7 Verilog Description for 1-bit Full Adder |  |  |  |  |  |  |

|------------------------------------------------------|--|--|--|--|--|--|

| // Define a 1-bit full adder                         |  |  |  |  |  |  |

| <pre>module fulladd(sum, c_out, a, b, c_in);</pre>   |  |  |  |  |  |  |

| // I/O port declarations                             |  |  |  |  |  |  |

| output sum, c_out;                                   |  |  |  |  |  |  |

| input a, b, c_in;                                    |  |  |  |  |  |  |

| // Internal nets                                     |  |  |  |  |  |  |

| wire s1, c1, c2;                                     |  |  |  |  |  |  |

| // Instantiate logic gate primitives                 |  |  |  |  |  |  |

| xor (s1, a, b);                                      |  |  |  |  |  |  |

| and (c1, a, b);                                      |  |  |  |  |  |  |

| <pre>xor (sum, s1, c_in);</pre>                      |  |  |  |  |  |  |

| and (c2, s1, c_in);                                  |  |  |  |  |  |  |

| <pre>xor (c_out, c2, c1);</pre>                      |  |  |  |  |  |  |

| endmodule                                            |  |  |  |  |  |  |

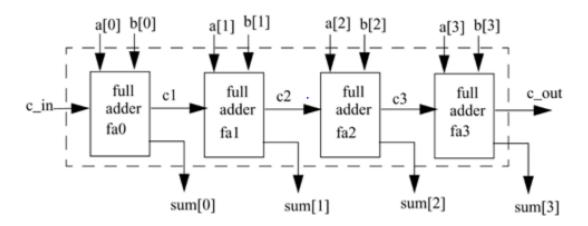

A 4-bit ripple carry full adder can be constructed from four 1-bit full adders, as shown in Figure 3-7. Notice that fa0, fa1, fa2, and fa3 are instances of the module fulladd (1-bit full adder).

Figure 3-7. 4-bit Ripple Carry Full Adder

This structure can be translated to Verilog as shown in Example 3-8. Note that the port names used in a 1-bit full adder and a 4-bit full adder are the same but they represent different elements. The element sum in a 1-bit adder is a scalar quantity and the element sum in the 4-bit full adder is a 4-bit vector quantity. Verilog keeps names local to a module.

Names are not visible outside the module unless hierarchical name referencing is used. Also note that instance names must be specified when defined modules are instantiated, but when instantiating Verilog primitives, the instance names are optional.

## Example 3-8 Verilog Description for 4-bit Ripple Carry Full Adder

```

// Define a 4-bit full adder

module fulladd4(sum, c_out, a, b, c_in);

// I/O port declarations

output [3:0] sum;

output c_out;

input[3:0] a, b;

input c_in;

// Internal nets

wire c1, c2, c3;

// Instantiate four 1-bit full adders.

fulladd fa0(sum[0], c1, a[0], b[0], c_in);

```

```

fulladd fa1(sum[1], c2, a[1], b[1], c1);

fulladd fa2(sum[2], c3, a[2], b[2], c2);

fulladd fa3(sum[3], c_out, a[3], b[3], c3);

endmodule

```

Finally, the design must be checked by applying stimulus, as shown in Example 3-9. The module stimulus stimulates the 4-bit full adder by applying a few input combinations and monitors the results.

## Example 3-9 Stimulus for 4-bit Ripple Carry Full Adder

```

// Define the stimulus (top level module)

Kree th

module stimulus;

// Set up variables

reg [3:0] A, B;

reg C_IN;

wire [3:0] SUM;

wire C OUT;

t FA1 4

// Instantiate the 4-bit full adder

fulladd4 FA1 4(SUM, C_OUT, A, B

signal values

initial

begin

$monitor($time," A= %b, B=%b, C IN= %b, --- C OUT= %b, SUM= %b\n",

A, B, C IN, C OUT, SUM);

end

// Stimulate inputs

initial

begin

A = 4'd0; B = 4'd0; C IN = 1'b0;

#5 A = 4'd3; B = 4'd4;

Dept.of ECE/ATMECE, Mysuru

```

#5 A = 4'd2; B = 4'd5; #5 A = 4'd9; B = 4'd9; #5 A = 4'd10; B = 4'd15; #5 A = 4'd10; B = 4'd5; C\_IN = 1'b1; end

endmodule

The output of the simulation is shown below.

0 A= 0000, B=0000, C\_IN= 0, --- C\_OUT= 0, SUM= 0000 5 A= 0011, B=0100, C\_IN= 0, --- C\_OUT= 0, SUM= 0111 10 A= 0010, B=0101, C\_IN= 0, --- C\_OUT= 0, SUM= 0111 15 A= 1001, B=1001, C\_IN= 0, --- C\_OUT= 1, SUM= 0010 20 A= 1010, B=1111, C\_IN= 0, --- C\_OUT= 1, SUM= 1001 25 A= 1010, B=0101, C\_IN= 1, --- C\_OUT= 1, SUM= 0000

# **3.3 Gate Delays**